다석식회로에서의 편여자현상 방지대책

다석식회로에서의 편여자현상 방지대책

1.다석식 회로의 개요

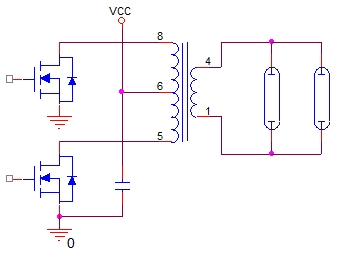

다석식 회로란 스위칭 Gate소자가 하나이상 사용되는 회로를 말하는데 Push-Pull / Half-Bridge / Full-Bridge회로를 다석식 회로로라 할 수 있다. 다석식회로의 경우 대용량의 Power설계가 가능하다는 장점은 있으나 두개 이상의 Switching소자를 사용하는 관계로인하여 Trans1차측에 편여자현상을 유발하여 Trans가 포화되는 현상을 방지할 수 있는 안전장치가 필요한다.

Push-Pull회로의 경우 두스위칭소자의 Turn-On간에 Dead Time를 설정하여 편여자현상을 방지할 수 있고, Half-Bridge 및 Full-Bridge회로의 경우 Blocking Cap을 삽입하여 방지할 수 있다.

이 경우 Push-Pull에서 Dead Time를 적용할 경우 Power제어의 한계가 주어지는 Demerit이 있고, Blocking Cap의 사용시 Cap에 의한 손실의 Demerit이 존재한다.

※따라서 편여자 현상에 대한 문제는 검토를 해보니 “있다/없다”의 문제가 아니라 만일의 경우 “발생했을 경우 편여자를 방지할 수 있는 안전장치가 있느냐 없느냐”의 문제로 접근해야 함.

< Fig01. Full Bridge >

< Fig02. Half Bridge >

< Fig03. Push-Pull (Direct) >

2.편여자현상의 개요

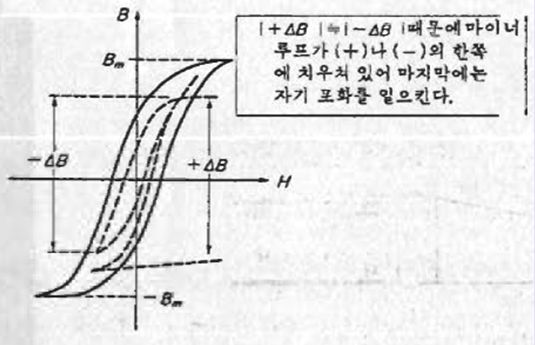

< Fig04. 트랜스의 편여자 현상 >

< Fig05. 자속밀도 변동율 >

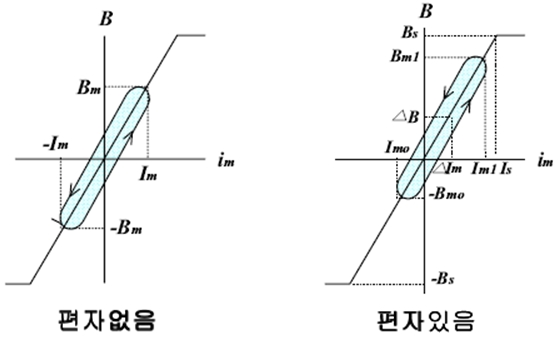

B-H곡선의 자속 밀도 변화는 상승하는 변화분과 하강하는 변화분 등이 같아야 한다. 하지만 2개의 스위칭 트랜지스터의 축적 시간 tstg에 불균형이 있으면 반드시 이렇게 되지 않고 자속 밀도가 상하 어느 쪽으로 치우친다.

베이스의 구동 신호는 Tr1과 Tr2 모두 같은 시간폭으로 되어 있기 때문에, 예를 들어 Tr1의 tstg가 Tr2에 비교하여 길다고 하면 그림(Fig04)과 같이 상승분 △B가 하강분 -△B보다 큰 값이 된다. 그 때문에 자속 밀도는 스위칭의 1주기마다 (+)측으로 치우치고 마침내 Bm을 넘어 자기포화를 일으킨다. 이것을 편여자 현상이라고 한다.

3.다석식회로에서의 편여자현상 방지대책 – Push-Pull회로

< Fig06. 트랜지스터의 축적 시간과 양점고 현상 >

Push-Pull회로의 경우 양 Trans의 Turn-On시간사이에 Dead Time을 어느 정도 설정함으로써 편여자 현상을 방지할 수 있다.

4.다석식회로에서의 편여자현상 방지대책 – Full Bridge, Half Bridge회로

< Fig07. 편여자의 방지 방법 >

Bridge회로의 경우 Blocking Cap을 사용하여 편여자 현상을 방지할 수 있다.

'공사교육자료 > 전기 - 공사교육' 카테고리의 다른 글

| 전자부품 저항의 종류 및 특징 (0) | 2025.11.18 |

|---|---|

| 각 콘덴서의 종류 및 특징 (0) | 2025.11.17 |

| PID제어 전동기 제어계의 구성 (0) | 2025.11.13 |

| PCB 칩의 맨하탄 현상(Manhattan phenomenon)의 원인과 대책 (0) | 2025.11.12 |

| 큐비클 내부 Cooling Fan 용량 산출 (0) | 2025.11.11 |