논리게이트(Logic Gate) 및 플립플롭(Flip Flop)의 종류

논리게이트(Logic Gate) 및 플립플롭(Flip Flop)의 종류

1. 논리 게이트

1) Buffer 회로

이는 일반적으로 타 회로와 접속시 Impedance 매칭을 위한 회로로 많이 이용되는 게이트로서 입력된 신호가 변화 없이 출력되며 또한 입력단자가 하나이고 출력단자가 하나여서 논리 게이트 라 볼 수는 없으며 단순한 게이트라 볼 수 있다. 논리(Logic) 게이트란 반드시 입력단자가 2개 이상의 게이트여야 하는 것이다

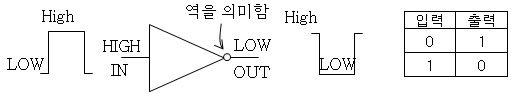

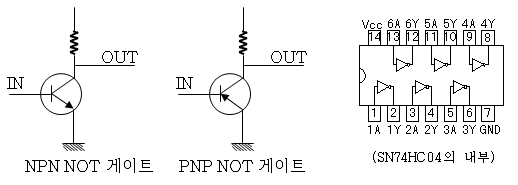

2) NOT회로

NOT회로는 일반적으로 반전 또는 보수를 행하는 기본논리 함수로 보통 인버터(inverter)라 부른다. 인버터의 목적은 하나의 논리 레벨을 다른논리의 레벨로 변환 하는 것이다.

※ SN74 시리즈의 IC에는 74 다음에 LS라든가 HC라는 문자가 붙어 있는데 이 의미는 LS(Low power Shotkey)는 저소비전력을 나타내고 있으며, HC는 CMOS Type으로 만들어지고 있는 것으로, 더욱 저소비 전력이다.

예) SN7400 ->22㎃ SN74LS00 ->4.4 ㎃ SN74HC00-> 0.02 ㎃

모든 종류의 IC에 LS라든가, HC라는 문자가 없는 것은 bipolar 타입이다.

3) AND 게이트 회로

※ Q = A x B

AND 게이트는 2 이상의 입력단자와 단일출력으로 구성되었다. 즉 1개의 게이트는 입력단자가 2, 3, 4, 8 및 2개 이상이라도 출력단자는 하나인 것이다. AND 게이트의 기본연산은 모든 입력이 High레벨 일 때만 출력이 High레벨이고 어떤 입력 한 개라도 Low이면 출력은 Low이다.

4) OR 게이트

※ Q = A + B

OR 게이트도 AND 게이트와 같이 두 개 또는 그 이상의 입력과 출력을 갖는다. OR 게이트의 연산은 입력의 어느 하나라도 High이면 출력이 High가 되고 입력이 모두 Low일 때만 출력이 Low가 된다.

5) NAND 게이트

※ Q = A x B

NAND는 NOT_AND를 줄인 말로 AND출력을 인버트(반전)한 것이다. 이 연산은 출력에 한해서는 AND의 반대이다.

6) NOR 게이트

※ Q = A + B

NOR는 NOT-OR를 줄인 말이고 OR 함수의 출력을 인버트(반전)한 것이다.

A 또는 B , 둘 다 High이면 출력은 Low이다.

A 그리고 B가 모두 Low이면 출력은 High이다.

7) INHIBIT회로

2개 이상의 입력단자 중 H단자에만 “L”가 걸리고 나머지 모든 단자에 “H”가 걸릴 때에만 출력이 “H”가 되는 회로이다. 이 게이트는 특수한 경우에 사용한다

8) EXCLUSIVE_OR 게이트

이 게이트 회로는 두개의 입력이 서로 다른 경우에는 출력이 High 이고 입력이 서로 같은 경우에는 출력이 Low 가 되는 회로이다. 이 게이트 회로는 일명 반 일치 회로 또는 배타적 논리회로라고도 한다.

9) EXCLUSIVE_NOR 게이트

2. 플립 플롭

2개의 입력에 대하여 1개의 출력이 나오는 쌍 안정 멀티 바이브레이터를 플립 플롭(FLIP_FLOP)이라고도 하며 다른 입력이 가해지기까지 앞서의 상태를 계속 유지하는 기억 기능을 가지고 있어 디지털 회로에 많이 사용되고 있다.

1) RS플립 플롭

출력에는 기호 Q 를 사용하고, 이 출력 Q를 “H”로 하기 위한 입력단자를 세트(Set)입력단자, 출력 Q를 본래의 “L”로 되돌리기 위한 입력단자를 리세트(Reset)입력단자 라고 하며, 각각 기호를 S, R로 표시한다. 플립플롭에서는 Set입력과 Reset 입력을 동시에 인가하여 사용할 수가 없기 때문에 이때의 출력 Q에는 X를 붙인다.

2) RS플립 플롭의 NAND변환

3) Q 출력과 Q' 출력

플립 플롭 출력은 Q단자의 출력에 대하여 반대 출력이 얻어지며, 이 단자를 Q' 단자라고 한다.

4) R'S' 플립 플롭

위 좌측의 그림과 같이 인버터를 제거하면 “L”입력단자를 갖는 플립플롭이 되며, 이와 같은 것을 RS 플립 플롭이라고 한다. 일반적으로 많이 사용된다.

5) 동기식 플립 플롭

동기 입력단자(CLOCK)를 가지고 있고, 이 단자에 가한 클럭입력이 상승 또는 하강 시에만 동작한다. 또 클럭에 무관하게 출력을 “H”로 하는 프리셋트(Preset) 입력단자와 출력을 L 로 하는 클리어(Clear) 입력단자가 있다.

6) JK플립 플롭

JK플립 플롭은 J와 K의 2개의 입력단자를 갖고, 클럭이 들어올 때 J나 K의 값에 따라서 출력이 변한다.

- J가 Low이고, K가 Low이면 출력(Q)은 변하지 않는다

- J가 High, K가 High이면 출력(Q)은 반전한다.

'공사교육자료 > 전기 - 공사교육' 카테고리의 다른 글

| 제논 램프 (Xenon Lamp)의 파장특성 및 종류 (0) | 2023.04.03 |

|---|---|

| 계측기,멀티테스터(Multi Tester Meter) 사용방법 (0) | 2023.02.14 |

| 디지털 (Digital)과 아날로그 (Analog)의 차이점 / 디지털시스템의 특징 (0) | 2023.02.10 |

| 정전압 회로(Regulated Circuit)의 제어방식, 회로구성 설명 (0) | 2023.02.09 |

| 정류 회로(Rectifier)의 종류 / 단상반파정류회로, 양파 정류회로, 브리지 정류회로 등 (0) | 2023.02.08 |